基础知识之二——STA相关的基本定义

在前一部分介绍了什么是STA,STA在数字IC设计流程中的位置,优点。该博文继续介绍STA,先通过一个简单的例子来引入,然后介绍一些STA的有关定义。我们的目的是为了建立一个模型,将我们的Verilog HDL语言综合的Schematic原理图转换为数学模型,这样就能使用计算机来进行分析时序。从而可以保证时序收敛。

引例

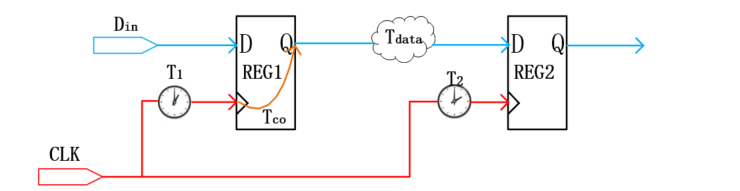

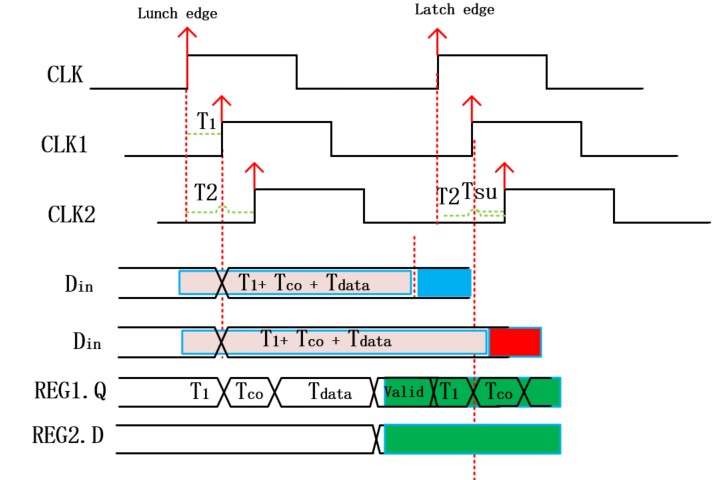

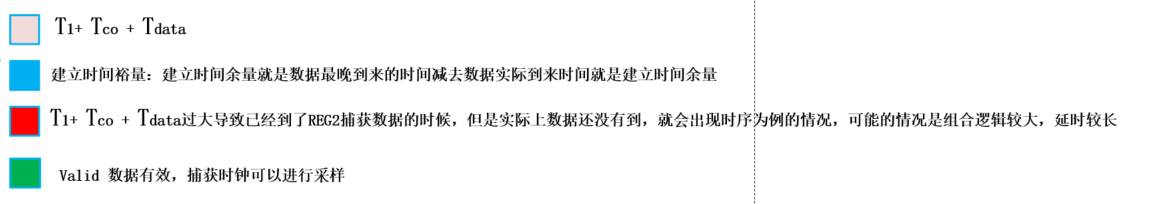

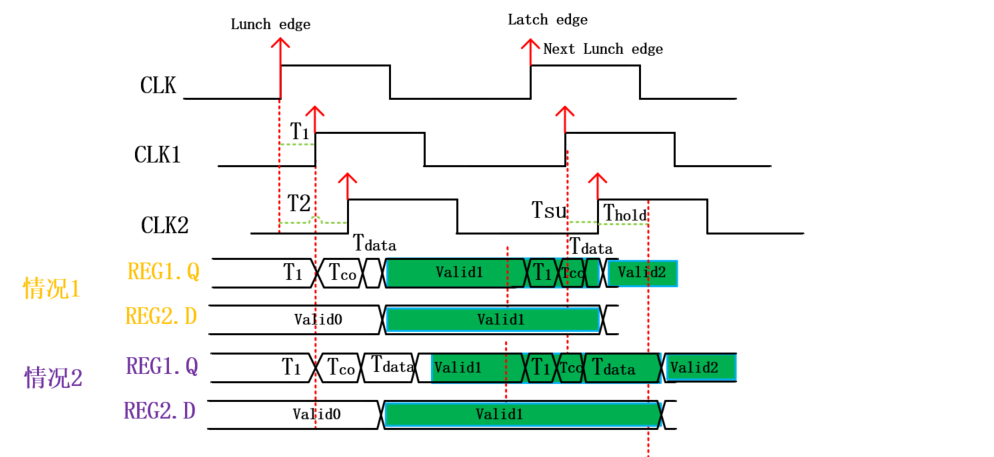

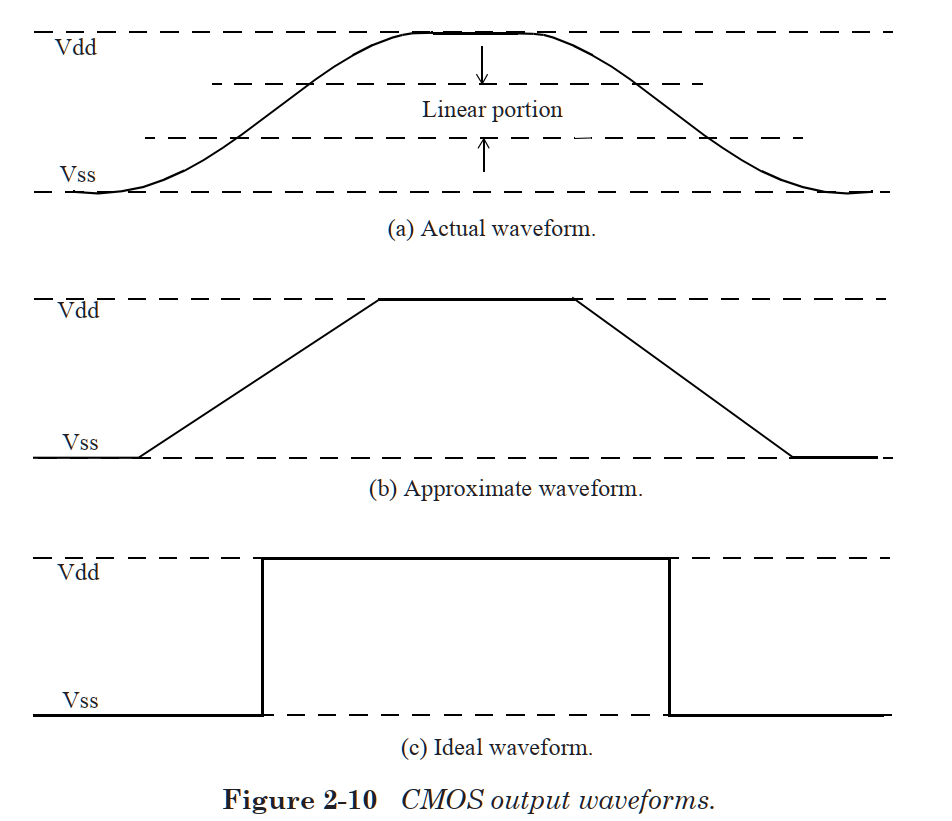

先看下面一个例子,先做一个简单的介绍,有没有接触过的定义会在后面进行介绍,主要是通过引例使得后面的定义更好理解。可以暂时不需要理解,但是看完本后可以通过这个引例来进一步进行学习。下面的几个图可以理解是时序分析的核心了,理解他们可以帮助理解很多问题

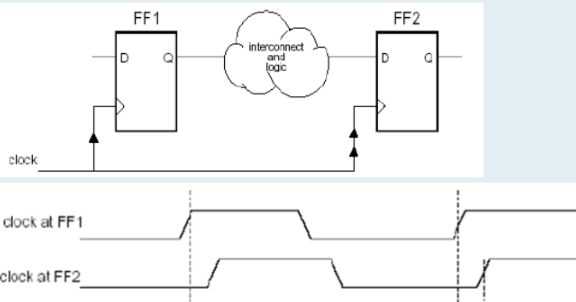

T1:为基准时钟与时钟到达一级寄存器的偏斜时间

T2:为基准时钟与时钟到达二级寄存器的偏斜时间

Tco:数据在寄存器中传输的延时

Tsu:建立时间,寄存器的时钟信号有效沿到来之前数据必须稳定的最小时间

Thold:保持时间,寄存器的时钟信号有效沿到来之后数据必须稳定的最小时间

Tdata:数据经过一级寄存器(或经过组合逻辑),进入二级寄存器输入端的延时时间

CLK1:基准时钟经过延时后达到一级寄存器的时钟

CLK2:基准时钟经过延时后达到二级寄存器的时钟

数据到达时间(Data arrival time):数据从D发送寄存器的D到接收寄存器的D端的时间 T1+ Tco+ Tdata

要求数据到达时间(Data Require time):根据两级寄存器的是时钟偏移,加上数据的建立时间,计算要求数据到达的时间(T-Tsu)+Tcycle。这里的数据到达时间计算以及数据到达时间的计算都是从基准时钟的发射沿开始计算的。

上边的是建立时间的例子,下面的图用来展示保持时间的例子。

对于情况1,由于数据到达时间太短了,数据还没有取到,而下一个数据已经来了,因此就会使得错过这个数据。

情况2是正常的保持时间的情况。

相关定义

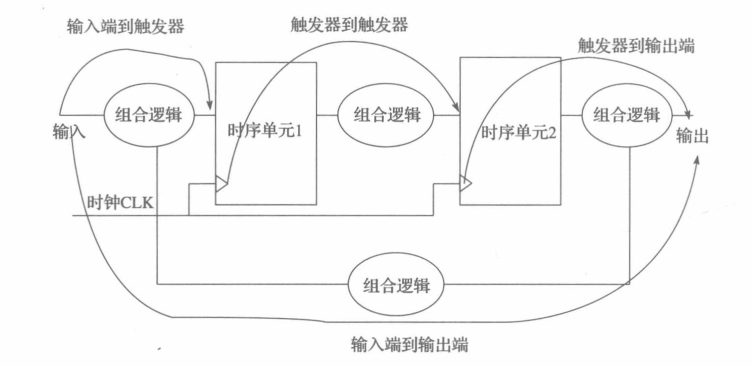

时序路径(timing path)

1:从输入端口到FF的D端;Input To Register

2:从FF1的CLK端到FF2的D端;Register To Register

3:从FF2的CLK端到输出端口;Register To Output

4:从输入端口到输出端口。 Input To Output,一般设计中这种情况是尽量避免的,具体原因在后续的学习中将会进行解释。

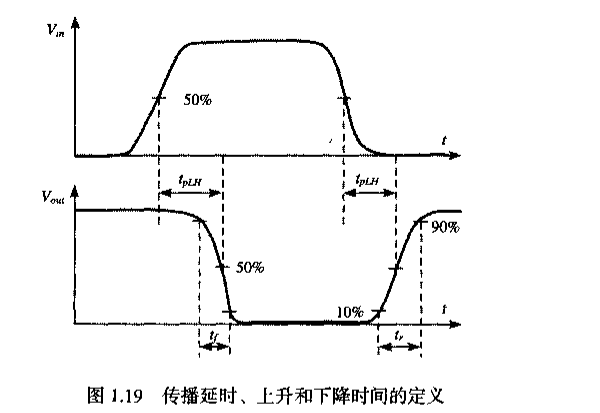

传播延时 propagation

本质上传播延时是一个人为定义的逻辑门质量指标,没有实际的物理意义。

举例如下:

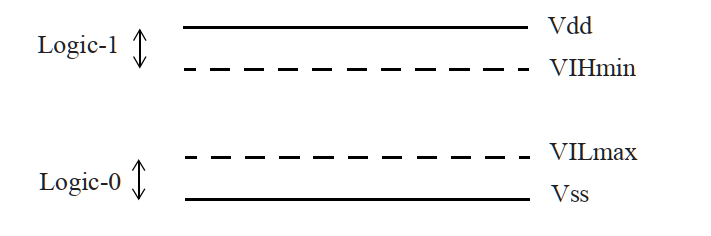

转换时间 transition

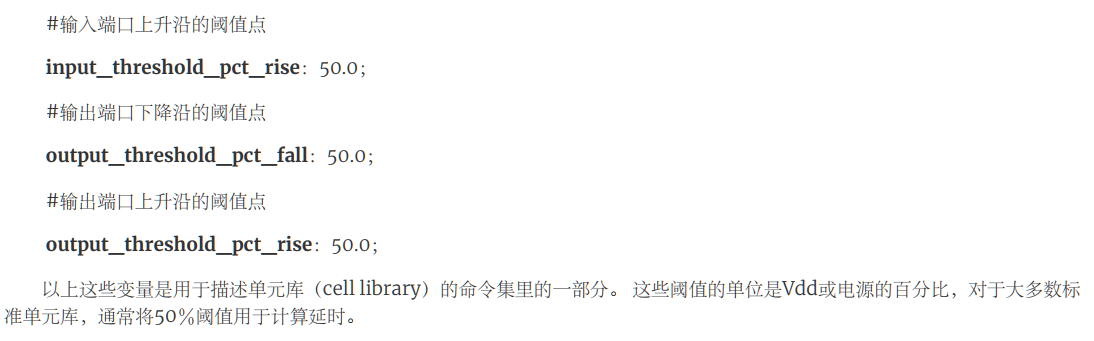

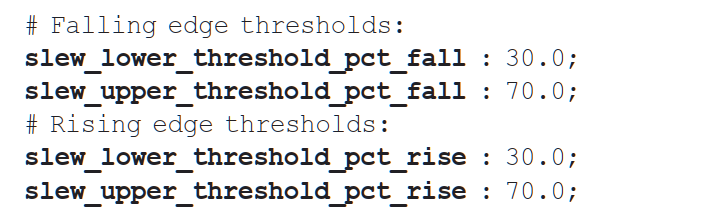

转换时间是指信号在两个特定电平之间转换所需要的时间。与之有关的是下降沿阈值与上升沿阈值的设置。如下所示。

时序弧

时序弧是静态时序分析的基础,静态时序分析是基于时序弧数据的时序分析。时序弧是用来描述两个节点之间的时序信息来定义的,一般分为连线延时与单元延时。

连线延时是单元输出端口和扇出网络负载之间的延时信息。1,理想导线2,集总模型3,集总RC模型4,分布式RC模型5,传输线模型等一些模型是用来计算RC的值的。至于为什么计算,参考补充定义的CMOS逻辑设计补充知识点部分,后续的博文还有有对其的解释与使用方式。

单元延时是单元输入到输出端口之间的延时。

逻辑通过逻辑路径传播的总延迟称为路径延迟(path delay),包括了逻辑路径中经过各个逻辑单元(cell)和网络走线(net)的延迟。

组合时序弧

组合时序弧是最基本的单元延时信息时序弧,主要用于表示组合逻辑单元的延时信息在时序信息文件中通过时序弧类型信息Combinational进行声明,如下所示。timing_type : combinational;

由于组合时序弧也是默认的时序弧类型,因此没有特别声明的时序弧就默认为组合时序弧。组合时序弧根据单元功能逻辑的不同,分为基于3种不同逻辑状态下的延时弧。

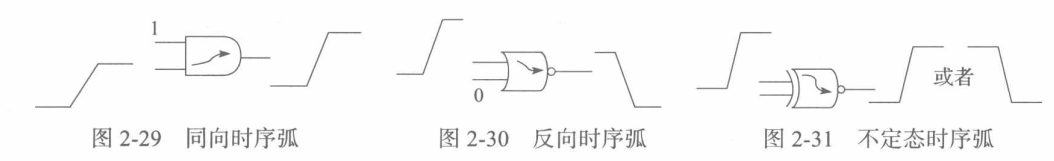

同向时序弧

同向时序弧表示输入端信号变化方向与输出端信号变化方向一致的时序弧

反向时序弧

反向时序弧表示输人端信号变化方向与输出端信号变化方向相反的时序弧

不定态时序弧

不定态时序弧表示输入信号变化方向与输出端信号变化方向无固定确定关系的时序弧

边沿时序弧

边沿时序弧用来表示时序单元从时钟信号有效沿到输出信号有效的延时信息。

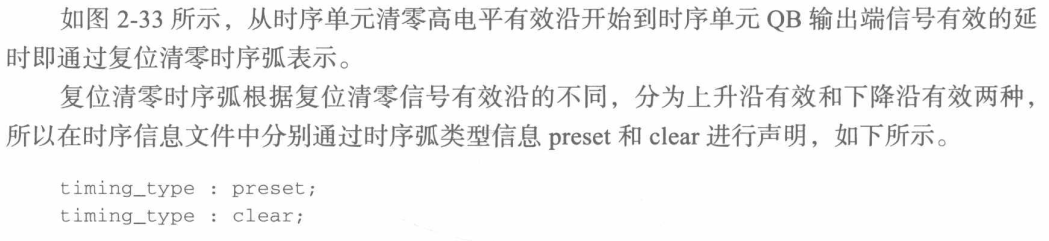

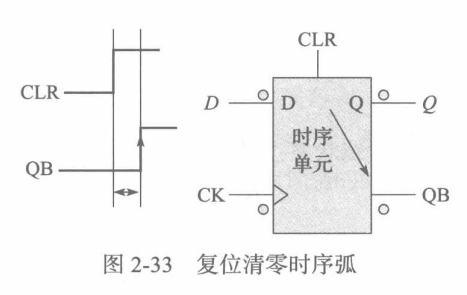

复位清零时序弧

复位清零时序弧用来表示具有复位清零端口的时序单元从复位清零信号有效沿到输出信号有效的延时信息。

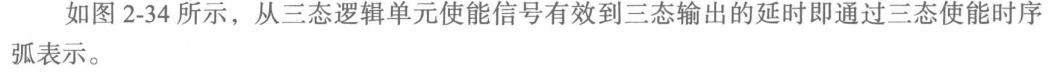

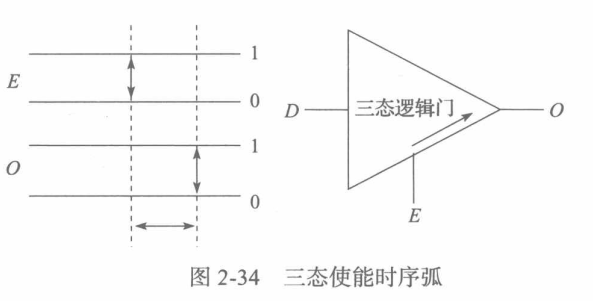

三态使能时序弧

三态使能时序弧用来表示三态逻辑单元从使能信号有效到输出的延时信息

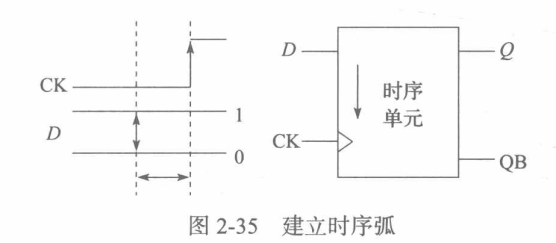

建立时序弧

建立时序弧用来表示时序单元获得正确数据信号所需要的约束信息,即在时钟沿有效前数据输入信号保持有效的时间信息。

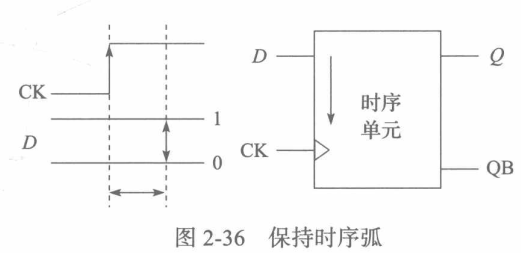

保持时序弧

保持时序弧也是用来表示时序单元获得正确信号所需要的约束信息,即在时钟沿有效后数据输入信号继续维持有效的时间信息。

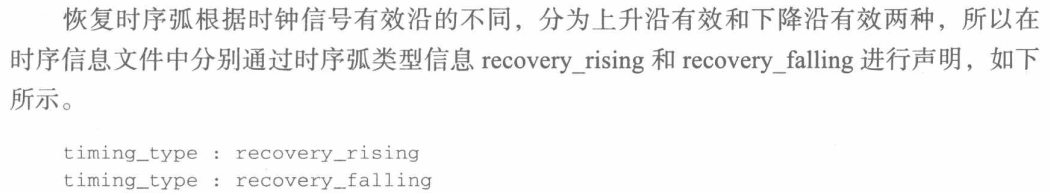

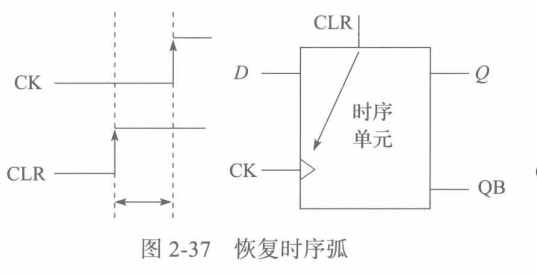

恢复时序弧

类似于复位的建立时间。恢复时序弧用来表示具有复位清零端口的时序单元成功使能所需要的约束信息,即在时钟沿有效前使能信号保持有效的时间信息。

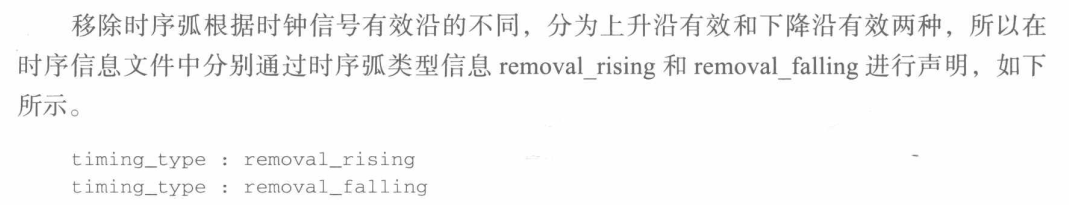

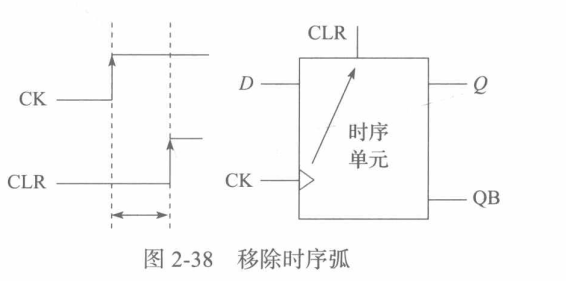

移除时序弧

移除时序弧也是用来表示具有复位清零端口的时序单元成功使能所需要的约束信息,即在时钟沿有效后使能信号维持有效的时间信息。

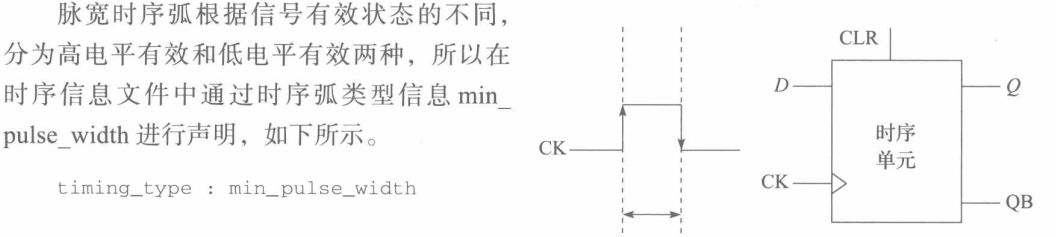

脉宽时序弧

脉宽时序弧也是用来表示时序单元获得正确信号所需要的约束信息,即时钟信号同一状态下维持有效的最小总时间信息。时钟信号脉冲过窄会导致时序单元本身无法工作,或是在组合逻辑路径传输中慢慢削弱而失真。

通过使用SDC命令set min pulse width来定义时钟信号的最小脉宽(minimum pulse width),示例命令如下:set_min_pulse_width-high 1.5[all_clocks]set_min_pulse_width-low 1.0[all_clocks]

以上命令定义所有时钟高电平最小脉宽为1.5s,低电平最小脉宽为1ns。

在后续的逻辑单元库的内容可以与之相互补充,这里再解释定义的同时其实对逻辑单元库进行了一部分的解释。

时钟有关的定义

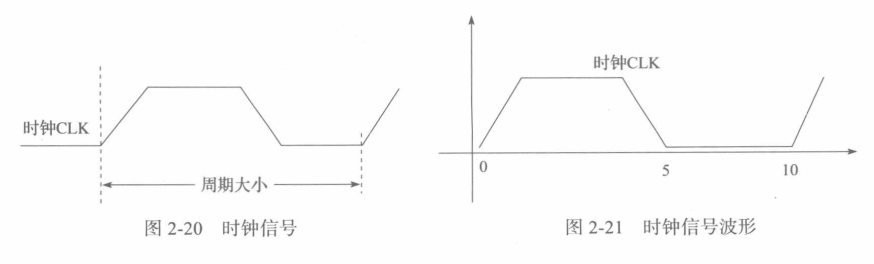

时钟周期

时钟周期也称为振荡周期,定义为时钟频率的倒数。

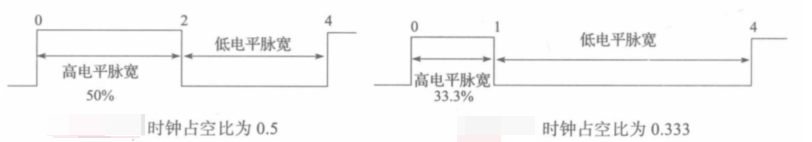

时钟占空比

时钟占空比是指时钟信号高电平在一个周期之内所占的时间比率,一般设计中,大部分的时钟占空比为50%,即占空比为0.5,说明高、低电平所占时间都为0.5个周期。但根据设计需要,也可以设计占空比不同的时钟信号。

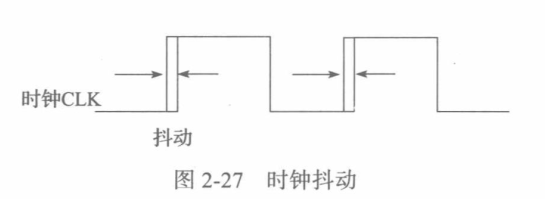

时钟抖动

指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生。可能是PLL等固有原因引起的。

时钟偏移

时钟偏斜(clock skew)是集成电路中一个时钟翻转的到达时间在空间上的差别(到达不同时钟树终点的时间差)。

可以使用set_clock_uncertainty命令显式指定时钟不确定度的值。在实现时钟树前,set_clock_uncertainty命令指定的值将包括时钟抖动、时钟偏斜估计值以及额外悲观度。看一个例子。

set_clock_uncertainty 0.2 [get_clocks USBCLK] |

上面这条命令中200ps的时钟不确定度可能是由50ps时钟抖动、100ps时钟偏斜以及50ps的额外悲观度组成的。

时钟延时

时钟延迟(clock latency)是指从时钟源到终点所花费的总时间。在逻辑设计的早期阶段,STA通常使用理想的时钟树来执行,因此分析的重点是数据路径(data path)

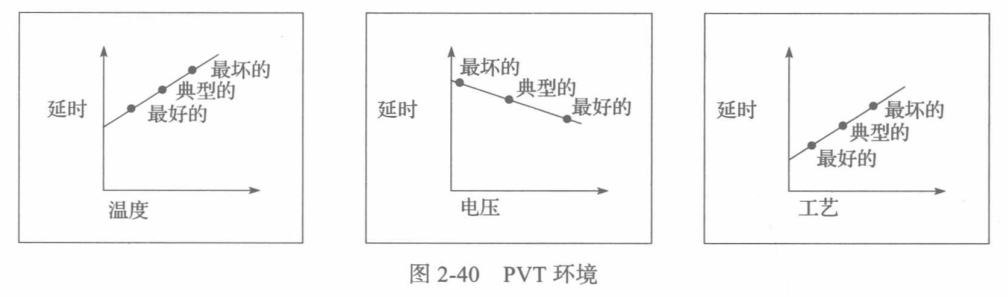

PVT环境

静态时序分析通常是在特定的工作条件(operating condition)下执行的,工作条件定义为工艺(process)、电压(voltage)和温度(temperature)的组合,简称PVT。

其中电压越高越好,温度越低越好,工艺偏差越小越好

半导体代工厂(foundry)为数字设计提供了3种加工工艺模型:慢速(slow)工艺模型,典型(typical)工艺模型和快速(fast)工艺模型,快速和慢速工艺模型代表了半导体代工厂加工的两个极端工艺角(process corner)。

可以使用set_operating_conditions命令明确指定设计的工作条件。

set_operating_conditions “WCCOM” -library mychip |

上述命令使用了在单元库mychip中定义的名为WCCOM的工作条件。

工艺角(工作条件)

WCS(Worst-Case Slow)

工艺慢(slow)、温度最高(例如125°C)并且电压最低(例如额定1.2V减去10%)

TYP(Typical)

典型(typical)工艺,温度是额定值(例如25°C),电压是额定值(例如1.2V)

BCF(Best-Case Fast)

工艺快(fast),温度最低(例如-40°C),电压最高(例如额定1.2V加10%)

功耗分析工作条件

ML(Maximal Leakage):工艺快,温度最高(例如125°C),电压也最高(例如1.2V加10%)。

该工作条件有最大的漏电功耗(leakage power),对于大多数设计,也有着最大的有效功耗(active power)。

TL(Typical Leakage):经典工艺,温度最高(例如125°C),电压是额定值(例如1.2V)

该工作条件下的漏电功耗比较具有代表性,因为由于正常工作时的功耗,芯片温度往往会更高。

补充定义

PAP

Power Area Performance 。这是一个需要进行折中的选择,你很难或者你不能做到这三个方面同时达到最优解。也是我们DC约束需要考虑的问题,也是你的约束应该体现的部分。在后续的学习中会进一步进行解释。

时序收敛

时序收敛(英语:Timing closure)是现场可编程逻辑门阵列、特殊应用积体电路等集成电路设计过程中,调整、修改设计,从而使得所设计的电路满足时序要求的过程。一般也会称这项工作为收时序。

CMOS逻辑设计补充知识点

说明:该部分对《数字集成电路:电路、系统与设计(第二版)》的数字部分进行总结,主要以反相器为代表的一些电路的典型性质,帮助理解后续的相关概念,具体学习可以参考该部分的内容

CMOS逻辑电平

一般的逻辑电平就是0-1.是我们数字电路中可以接收的两种状态。

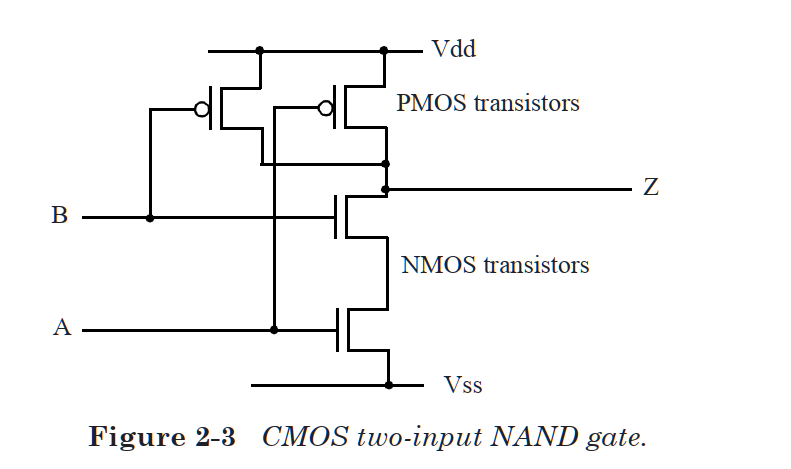

标准单元举例

看一个两输入与非门的定义

使用P做上拉网络,N管做下拉网络。由于其本身的强1弱0以及强0弱1的性质决定的。同时解释了我们为什么需要做一个布尔表达式的转换,就是由于基本单元都是与非门或非门这种形式,一个与门实际上是由6个管子(与非门四个+反相器两个)来构成的。

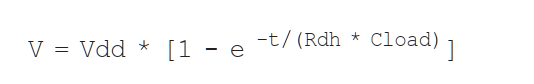

电平转换时间公式

对于一个单元的时序关系,可以看到这里的转换时间与两个因素有关,负载电容与电阻有关,这就是是RC在电路中的影响,对于单元延时的影响。当然主要是C,因为R已经确定了,但是你的负载是不确定的。

因此在DC中确定一个单元延时的方式就是根据其负载电容来查表获取的。

其次影响一个单元延时的还有输入转换时间。因为我们输出的负载确定了,但是你的输入转换时间也是对单元延时有影响的。

我们总结一下就是这几个因素:

- 内部:

- 单元本身的电阻

- 外部:

- 单元的负载

- 单元的输入转换时间

- 其他(通过设置缩放因子来解决)

- 制成

- 温度

- 电压……

我们在后续的学习中都会见到对其进行的建模的相关指令

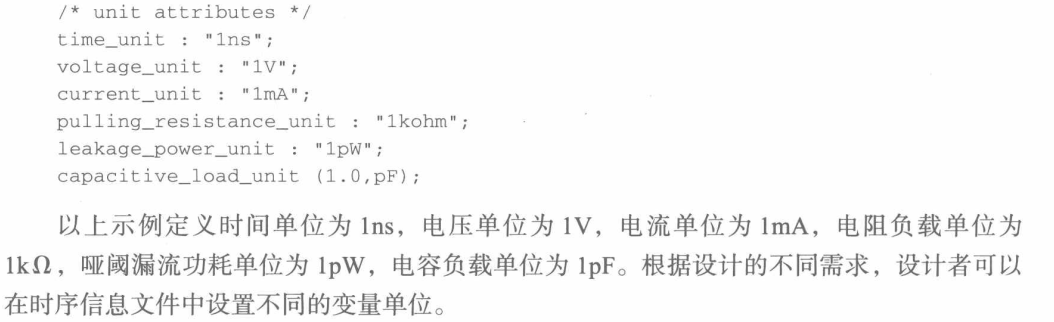

时序计算单位

时序分析中需要基于温度、电压、电流、电阻、电容负载和时间等不同类型的变量因子进行计算,因此需要在时序信息文件中定义不同类型的变量因子的单位。以下为时序信息文件中所定义的变量因子单位:

该部分会在第三节的单元库学习中进一步学习。

查看库的信息

举例read_db <target_library_FILE> 读入一个库文件list_libs 确定与该库文件对应的库的名称redirect -file lib.rpt {report_lib cb13fs120_tsmc_max} 为上述的库生成一个库报告文件

这里我们使用重定向的命令,将报告的结果保存到lib.rpt这个文件中。redirect是重定向的命令,-file是将命令产生信息保存到文件中,lib.rpt是要保存信息到文件,后面的{}中存放的是要执行的命令。